# **Integrated JPEG CODEC**

| Features                                                                                                                                                                                                                                                                                                                                                                | 1                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Introduction The ZR36060. The ZR36060 and the JPEG Standard JPEG baseline overview. JPEG markers Motion JPEG Notational Conventions                                                                                                                                                                                                                                     | 3                                                         |

| Pin Description                                                                                                                                                                                                                                                                                                                                                         |                                                           |

| Video Syncs - Master and Slave Modes  Master mode Slave mode Data Formats Video stream sampling and cropping The PVALID control signal Video Scaling Horizontal down-scaling in compression Vertical down-scaling in compression Horizontal up-scaling in decompression Vertical up-scaling in decompression Active Area Size Restrictions Spatial Mix of Video Streams | 8<br>9<br>9<br>10<br>. 11<br>. 11<br>. 12<br>. 12<br>. 12 |

| Host Interface                                                                                                                                                                                                                                                                                                                                                          |                                                           |

| Interrupt Request and Associated Registers                                                                                                                                                                                                                                                                                                                              |                                                           |

| Code Interface                                                                                                                                                                                                                                                                                                                                                          | _                                                         |

| Master Mode                                                                                                                                                                                                                                                                                                                                                             | 17<br>18<br>18<br>19                                      |

| Operation                                                                                                                                                                                                               | 21                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| ZR36060 Functional States                                                                                                                                                                                               | 21                                     |

| State Transitions                                                                                                                                                                                                       | 21                                     |

| The SLEEP State                                                                                                                                                                                                         | 21                                     |

| Loading Parameters and Tables                                                                                                                                                                                           |                                        |

| Data Flow Overview                                                                                                                                                                                                      |                                        |

| Data Flow in Compression                                                                                                                                                                                                |                                        |

| Data Flow in Decompression                                                                                                                                                                                              |                                        |

| Compression and Decompression Modes                                                                                                                                                                                     |                                        |

| Compression Pass                                                                                                                                                                                                        |                                        |

| Statistical Compression Pass                                                                                                                                                                                            |                                        |

| Auto Two-Pass Compression                                                                                                                                                                                               |                                        |

| Tables-Only Compression Pass                                                                                                                                                                                            |                                        |

| Decompression                                                                                                                                                                                                           |                                        |

| Data Corruption during Decompression                                                                                                                                                                                    |                                        |

|                                                                                                                                                                                                                         |                                        |

| Power Management and Power-up                                                                                                                                                                                           | 27                                     |

| Power Management and Power-up                                                                                                                                                                                           |                                        |

| Register and Memory Description                                                                                                                                                                                         | 28                                     |

| Register and Memory Description                                                                                                                                                                                         | <b>28</b><br>28                        |

| Register and Memory Description  General Control Registers  ID and Testing Registers                                                                                                                                    | <b>28</b><br>28<br>30                  |

| Register and Memory Description  General Control Registers                                                                                                                                                              | 28<br>30<br>31                         |

| Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers  JPEG Marker Segments.                                                                                            | 28<br>30<br>31<br>33                   |

| Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers  JPEG Marker Segments  Electrical Characteristics                                                                 | 28<br>30<br>31<br>33                   |

| Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers  JPEG Marker Segments.                                                                                            | 28<br>30<br>31<br>33                   |

| Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers  JPEG Marker Segments  Electrical Characteristics                                                                 | 28<br>30<br>31<br>33<br>35             |

| Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers  JPEG Marker Segments  Electrical Characteristics  Absolute Maximum Ratings                                       | 28<br>30<br>31<br>35<br>35             |

| Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers  JPEG Marker Segments.  Electrical Characteristics  Absolute Maximum Ratings  Operating Range  DC Characteristics | 28<br>28<br>30<br>31<br>35<br>35<br>35 |

| Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers  JPEG Marker Segments  Electrical Characteristics  Absolute Maximum Ratings  Operating Range                      | 28<br>30<br>31<br>35<br>35<br>35       |

#### **PRELMINARY**

# **INTEGRATED JPEG CODEC**

#### **FEATURES**

- Single-chip JPEG processor which integrates all the modules needed for JPEG encoding and decoding:

- Raster-to-block and block-to-raster converter

- Strip buffer

- JPEG codec

- Motion video compression and expansion capability:

- Up to 25 frames/sec, square pixel and CCIR PAL

- Up to 30 frames/sec, square pixel and CCIR NTSC

- Three modes of Bit Rate Control (BRC):

- Auto Two Pass: for still image compression, produces tightly controlled compressed data file size

- Single pass: for motion video compression, keeps the file size approximately fixed

- No BRC: uses fixed quantization tables

- Glueless interface to common video decoders (e.g., Philips, Brooktree, Samsung, ITT, Harris)

- Glueless interface to the ZR36057, I32 and other common multimedia controllers.

- Supports 8 and 16-bit YUV video interfaces

- Supports master and slave modes of video synchronization

- Interfaces to a variety of host controllers, ranging from the dedicated high-performance ZR36057 PCI controller to generic low-cost microcontrollers

- Flexible compressed data interface:

- 8-bit master mode, supporting transfer of up to 30 Mbytes/

- 16-bit slave mode, supporting transfer of up to 16.7 Mbytes/sec

- 8-bit slave mode, supporting transfer of up to 8.3 Mbytes/ sec

- On-chip video processing, including:

- Mixing of two video sources

- Horizontal (1:2 and 1:4) and vertical (1:2) up and down scaling

- Cropping in compression and programmable background color in decompression

- 3.3V power supply with 5V-tolerant I/O

- Low power consumption:

- 850 mW at 30 MHz operating frequency

- Power down mode for power saving

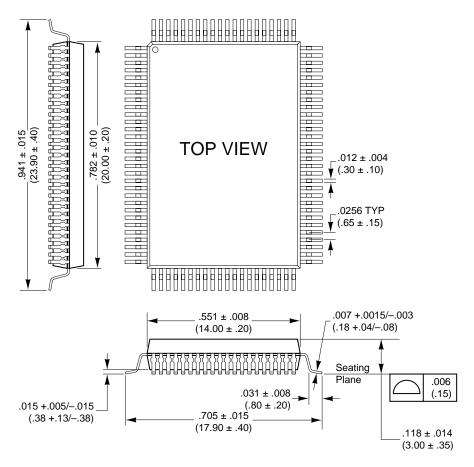

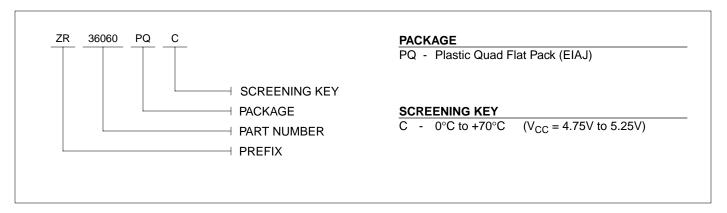

- 100-pin PQFP package

#### **APPLICATIONS**

- Desktop video editing subsystems

- PCMCIA video capture cards

- Digital still cameras

- Digital video recording

- JPEG-based video conferencing systems

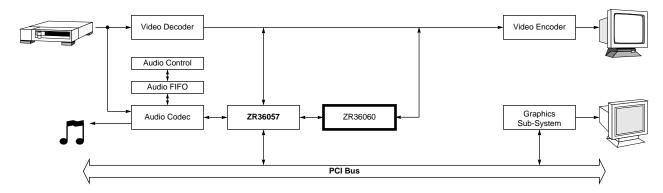

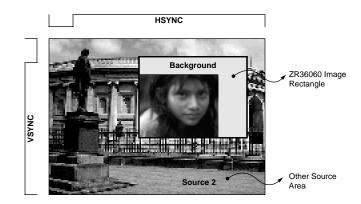

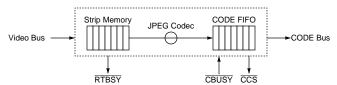

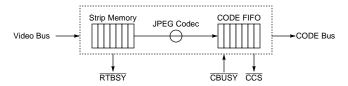

Figure 1. JPEG-based video editing subsystem for PCI Systems

# **Integrated JPEG CODEC**

# **Integrated JPEG CODEC**

| Features1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| The ZR36060 . The ZR36060 and the JPEG Standard JPEG baseline overview JPEG markers . Motion JPEG . Notational Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Video Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Video Syncs - Master and Slave Modes       6         Master mode       6         Slave mode       6         Data Formats       1         Video stream sampling and cropping       1         The PVALID control signal       10         Video Scaling       1         Horizontal down-scaling in compression       1         Vertical down-scaling in compression       1         Horizontal up-scaling in decompression       1         Vertical up-scaling in decompression       1         Active Area Size Restrictions       1         Spatial Mix of Video Streams       1 |

| Host Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interrupt Request and Associated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Code Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Master Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Operation                                                                                                                                                                                                                                             | 21                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| ZR36060 Functional States                                                                                                                                                                                                                             | . 21                                                           |

| State Transitions                                                                                                                                                                                                                                     |                                                                |

| The SLEEP State                                                                                                                                                                                                                                       |                                                                |

| Loading Parameters and Tables                                                                                                                                                                                                                         |                                                                |

| Data Flow Overview                                                                                                                                                                                                                                    |                                                                |

| Data Flow in Compression                                                                                                                                                                                                                              |                                                                |

| Data Flow in Decompression                                                                                                                                                                                                                            |                                                                |

| Compression Pass                                                                                                                                                                                                                                      |                                                                |

| Data Corruption during Compression                                                                                                                                                                                                                    |                                                                |

| Statistical Compression Pass                                                                                                                                                                                                                          |                                                                |

| Auto Two-Pass Compression                                                                                                                                                                                                                             | . 24                                                           |

| Tables-Only Compression Pass                                                                                                                                                                                                                          |                                                                |

| Decompression                                                                                                                                                                                                                                         |                                                                |

| Data Corruption during Decompression                                                                                                                                                                                                                  | 26                                                             |

|                                                                                                                                                                                                                                                       |                                                                |

| Power Management and Power-up                                                                                                                                                                                                                         |                                                                |

|                                                                                                                                                                                                                                                       | 27                                                             |

| Power Management and Power-up                                                                                                                                                                                                                         | 27<br>28                                                       |

| Power Management and Power-up                                                                                                                                                                                                                         | <b>27 28</b> . 28                                              |

| Power Management and Power-up                                                                                                                                                                                                                         | <b>27 28</b> . 28 . 30                                         |

| Power Management and Power-up                                                                                                                                                                                                                         | <b>27 28</b> . 28 . 30 . 31                                    |

| Power Management and Power-up  Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers                                                                                                                  | <b>27 28</b> . 28 . 30 . 31 . 33                               |

| Power Management and Power-up  Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers  JPEG Marker Segments.                                                                                           | 27<br>28<br>. 28<br>. 30<br>. 31<br>. 33                       |

| Power Management and Power-up  Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers  JPEG Marker Segments.  Electrical Characteristics                                                               | 27<br>28<br>. 28<br>. 30<br>. 31<br>. 33<br>35<br>35           |

| Power Management and Power-up  Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers  JPEG Marker Segments.  Electrical Characteristics  Absolute Maximum Ratings                                     | 27<br>28<br>. 28<br>. 30<br>. 31<br>. 33<br>35<br>35<br>35     |

| Power Management and Power-up  Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers  JPEG Marker Segments  Electrical Characteristics  Absolute Maximum Ratings  Operating Range  DC Characteristics | 27<br>28<br>30<br>31<br>33<br>35<br>35<br>35                   |

| Power Management and Power-up  Register and Memory Description  General Control Registers  ID and Testing Registers  Video Registers  JPEG Marker Segments.  Electrical Characteristics  Absolute Maximum Ratings  Operating Range                    | 27<br>28<br>28<br>30<br>31<br>33<br>35<br>35<br>35<br>35<br>36 |

#### 1.0 INTRODUCTION

#### 1.1 The ZR36060

The ZR36060 is an integrated JPEG codec targeted to video capture and editing applications in desktop and laptop computers. Figure 1 shows an example of a typical application, a video editing subsystem for PCI bus computers.

The ZR36060 integrates the functionality of a JPEG codec such as the ZR36050, a raster-to-block converter such as the ZR36015, as well as the strip buffer SRAM for the raster-to-block converter and additional functions. It is based on the field proven, fully compliant Zoran JPEG device technology, and incorporates Zoran's patented bit rate control mechanism.

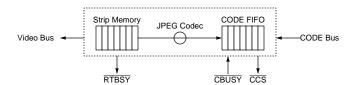

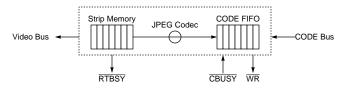

In compression, the ZR36060 accepts YUV 4:2:2 digital video, performs optional cropping and decimation, and encodes it into a JPEG baseline compressed bitstream, which it outputs to a host controller. In decompression, it receives the bitstream from the host controller, decodes it back to YUV 4:2:2 format digital video, up-scales it if required, and outputs the video to a composite video encoder or other destination.

The ZR36060 incorporates hardware support for multiplexing two video sources (in rectangular windows) in compression, or the reconstructed video with another source in decompression. It can operate as a video sync master or slave, with 8-bit or 16-bit video bus widths. A pixel flow control mechanism is provided for convenient implementation of non-real-time video rates, such as for still picture compression.

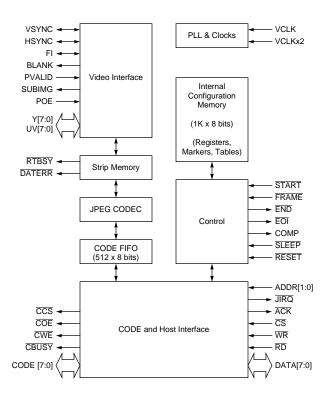

Figure 2. ZR36060 Block Diagram

The code interface of the ZR36060 can operate in 8-bit master, 8-bit slave or 16-bit slave modes. In slave mode, code transfer shares the host interface, which is generic enough to be able to interface gluelessly with a variety of host controllers, ranging from the dedicated, high performance ZR36057 to common microcontrollers.

The ZR36060 is a CMOS device, requiring a 3.3 Volt power supply. Its inputs and outputs are 5 Volt tolerant. A power-down ("sleep") mode reduces current consumption to a very low level, while preserving the logic state of the device.

A block diagram of the ZR36060 is shown in Figure 2.

#### 1.2 The ZR36060 and the JPEG Standard

The JPEG standard, ISO/IEC 10918-1, defines a whole range of options for compressing continuous-tone images - a baseline lossy compression process, extended lossy processes, lossless compression, and hierarchical compression methods. The ZR36060 implements the baseline process.

Even the baseline method is defined by the JPEG standard to provide maximal flexibility in choosing the color space in which an image is compressed - an image can have an almost unlimited number of color components, and these can be compressed in a single scan, or in multiple scans. Because its main targeted application is motion color video compression and decompression, the architecture of the ZR36060 supports one particular subset: Since the ZR36060 supports only the YUV 4:2:2 pixel format, it supports three color components, in a single interleaved scan.

#### 1.2.1 JPEG baseline overview

The JPEG baseline compression method is based on the discrete cosine transform or DCT. The DCT is performed on 8x8 blocks of samples, of each color component, resulting in a set of 64 DCT coefficients for each block. Thus, in order for a normal raster-scanned image to be compressed, it must first be converted to block format This requires that an 8-line strip of the image (containing 8 lines of each color component) be stored in a strip buffer, so that the samples can be re-ordered (see Figure 2).

For subsequent stages of the compression, the 64 DCT coefficients of each block are further re-ordered by scanning the block in a zig-zag sequence. Each of the 64 coefficients is quantized using the appropriate value from a 64-entry quantization table. In the ZR36060, it is possible to define three different quantization tables, one per color component; generally, however, two tables are used, one for the luminance component and one for the chrominance component.

The quantized DCT coefficients are passed to a Huffman encoder, for the final stage of the process. The Huffman coding is performed separately for the DC coefficient of each block (the first coefficient of the block), and the remaining 63 AC coeffi-

cients. The encoding methods used for DC and AC coefficients differ in their details, and this requires two Huffman tables to be specified, one for DC and one for AC. And since the statistics of the luminance and chrominance components are generally quite different, separate Huffman tables are required for luminance and chrominance, for a total of four tables, two DC and two AC. The ZR36060 supports this configuration.

Baseline decompression essentially consists of the inverses of each of the stages used in compression, in reverse order: Huffman decoding, dequantization, inverse DCT, and conversion of the blocks back to raster order.

#### 1.2.1.1 The Minimum Coded Unit

If the compressed image data is interleaved, as is the case in the ZR36060, the compression is performed in units of a Minimum Coded Unit, or MCU, which contains one or more blocks of each color components. For the 4:2:2 pixel format used by the ZR36060, where the chrominance (U and V) components are decimated by 2:1 horizontally relative to the luminance (Y), the MCU consists of 2 blocks of Y followed by one block each of U and V.

#### 1.2.1.2 Restart Intervals

The ZR36060 supports compression and decompression of JPEG data that includes restart intervals. A restart interval is defined as an integral number of MCUs, which are processed as an "independent sequence", meaning that it is possible to identify and decode a restart interval within a JPEG data sequence, without the need to decode whatever data precedes it. In the context of baseline compression, this has significance because the DC coefficients of the DCT are differentially encoded. Note that the use of restarts is optional; it is acceptable (and very common) to use no restart markers and encode the whole image as a single sequence.

#### 1.2.2 JPEG markers

JPEG defines three data formats for the compressed bitstream, all of which are supported by the ZR36060:

- The *interchange* format, which contains the specifications of all the tables required to decode the image.

- the abbreviated format for compressed data, which can contain some or none of the tables, under the assumption that

the remaining tables are known to the decoder and are already loaded in the decoder or can be loaded. This is

commonly used for motion video, in order to save the time

otherwise required to decode the tables from their

specifications.

- the abbreviated tables-only format, which contains no compressed data but only tables. It is one means by which it is possible to load tables into the decoder; in the ZR36060 the other means is by specifying the tables to the device and issuing an explicit Load command.

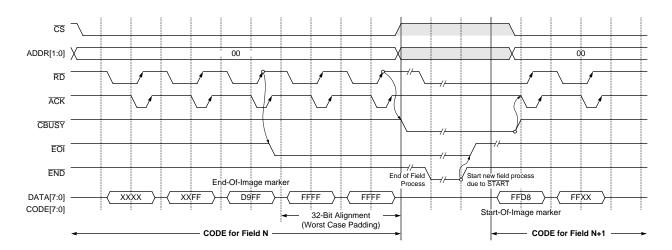

In all three of the formats, the tables and the parameters required for decoding the image and/or the tables are contained in *marker segments*, which are sequences of bytes that start with special two-byte codes called *markers* or *marker codes*. The two bytes that follow the marker specify the length of the marker segment in bytes, including the two length bytes but not including the marker code itself. There are two special stand-alone markers that are not associated with marker segments, to mark the start-of-image (SOI) and end-of-image (EOI). The code values are 0xFFD8 for SOI, and 0xFFD9 for EOI.

The first byte of every marker is 0xFF. A marker may be prefixed by an arbitrary number of 0xFF bytes which are discarded by the decoder. The second byte of a marker has defined values, except for 0x00, which is used as follows. In order to permit a decoder to identify the restart markers, if they exist, and the EOI marker, the encoder stuffs a 0x00 byte after every 0xFF byte that results from the Huffman encoding. Note that this "byte stuffing" is an essential part of the JPEG standard, and there is no definition in the standard of a bitstream that does not include the byte stuffing. The ZR36060 always produces image bitstreams with byte stuffing, and requires the byte stuffing to be present in order to decode a JPEG bitstream.

The JPEG standard also does not define any sort of "markerless" bitstream data format. Certain markers and marker segments are defined in the standard to be "required", and others, such as the restart markers and the table marker segments, are optional. The ZR36060 always includes the required markers when it produces a compressed bitstream, and can be programmed to include certain optional markers. To be decompressed by the ZR36060, an image bitstream *must* include the required markers. All markers included in the bitstream, required and optional, are handled automatically, without host intervention, by the ZR36060 in decompression.

# 1.2.2.1 Required markers and marker segments

The required markers for baseline JPEG are:

- Start-of-image, SOI (0xFFD8). This is the first marker in a JPEG image bitstream.

- Start-of-frame marker segment, SOF0 (0xFFC0), followed by a variable number of bytes depending on the number of color components. For the ZR36060, there are always three components and the segment has a length of 17 bytes. The SOF segment is used to specify which quantization table to use for each color component, and the number of blocks of each color component in the MCU.

- Start-of-scan marker segment, SOS (0xFFDA), followed by a variable number of bytes depending on the number of color components. The Huffman coded data follows immediately after the last byte of the SOS segment. In the case of the ZR36060, the length of the SOS segment is always 12 bytes. The SOS segment is used to specify which Huffman table to use for each color component.

End-of-image, EOI (0xFFD9). This marker follows the last byte of the compressed data.

#### 1.2.2.2 Optional markers and marker segments

The ZR36060 supports the following optional markers and segments:

- Application specific, APPn (0xFFE0-0xFFEF). The standard allows up to 16 different APP markers in a single image bit-stream. The ZR36060 can insert one APP marker in compression. A ZR36060 APP marker can have a segment length of up to 62 bytes. In decompression, if the image bit-stream contains a single APP marker with a segment length of 62 bytes or fewer, the host can retrieve it after the ZR36060 has finished decompressing the image; if the segment is longer, the data is lost. If there are multiple APP segments, only the last one can be retrieved.

- Comment, COM (0xFFFE). The restriction on the length (62 bytes) is the same as for the APP marker.

- Define restart interval, DRI (0xFFDD). Defines that restarts are to be used, and the size in MCUs of the restart interval.

- Define quantization tables, DQT (0xFFDB). Specifies the quantization tables used to compress the image.

- Define Huffman tables, DHT (0xFFC4). Specifies the Huffman tables used to compress the image.

- Restart, RSTm (0xFFD0-0xFFD7). Marks the beginning of a restart interval in the compressed data.

Note that when quantization and Huffman tables are loaded into the ZR36060 by the host controller, they are specified in exactly the same format as is used in the marker segments. In compression, the ZR36060 inserts optional marker segments, if programmed to do so, into the compressed data bitstream in a fixed order: APP, COM, DRI, DQT, DHT. These appear immediately after SOI, before SOF. In decompression, they can appear in any order or position allowed by the JPEG standard.

#### 1.2.3 Motion JPEG

The JPEG standard defines a method for compression of a single ("still") image. It does not have any provision for motion video, and the term "motion JPEG" simply means that each field of a video sequence is compressed as a separate JPEG image bitstream. The ZR36060 includes features that make this procedure straightforward.

#### 1.3 Notational Conventions

The following notational conventions are used in this data sheet:

External signals: bold capital letters (e.g., COMP)

Active-low mark: overbar (e.g., RESET)

Buses: XXmsb\_index:lsb\_index (e.g., UV7:0)

Register fields: XXmsb\_index:lsb\_index (e.g., Count27:16)

Register types:

- R read only

- · W write only

- RW read-write (data written can be read back)

Numbers: numbers with no prefix or suffix are decimal (e.g., 365, 23.19). Hexadecimal numbers are indicated with a '0x' prefix (e.g., 0xB000, 0x3). Binary numbers are indicated with a 'b' suffix (e.g., 010b, 0000110100011b).

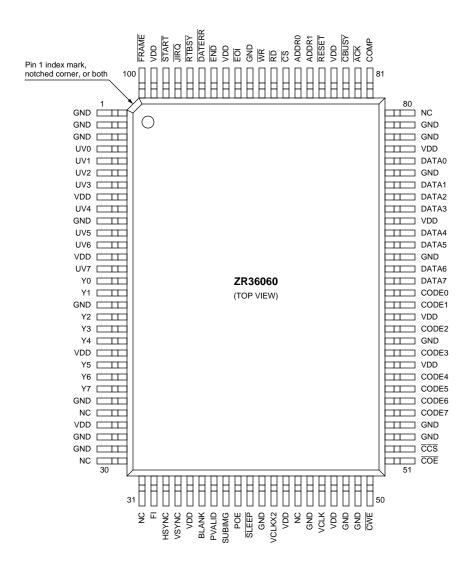

# 2.0 PIN DESCRIPTION

The ZR36060 is supplied in 100-pin PQFP package. The following table lists the pins of the device and provides a concise

functional description of each.

# **Table 1: Pin Descriptions**

| Symbol     | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Code/Host  | Port (2 | 6 pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

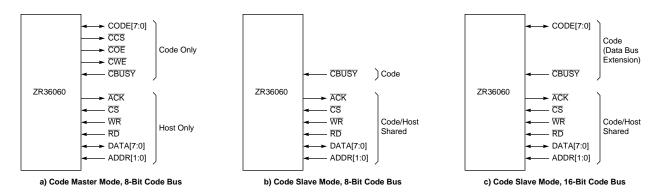

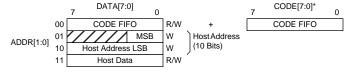

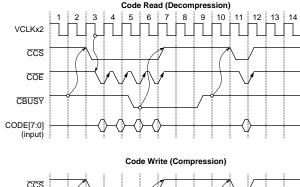

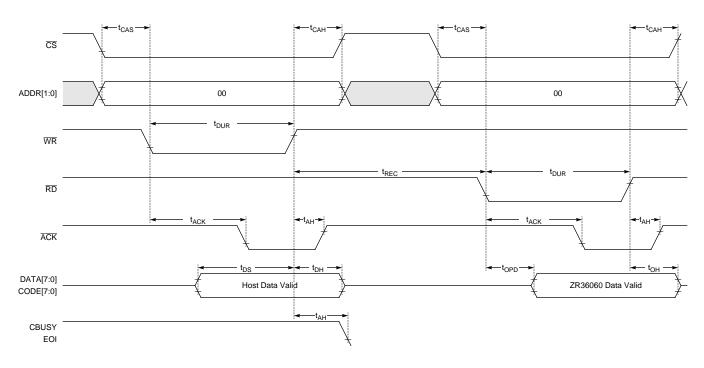

| CODE[7:0   | I/O     | Code bus. In Code Master mode, this 8-bit bidirectional bus is used to read (write) the compressed data from (to) an external code FIFO.  In 16-bit Code Slave mode, this is used as an extension (the MSB) of the DATA bus.  During and after RESET this bus is floating, with internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

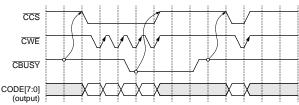

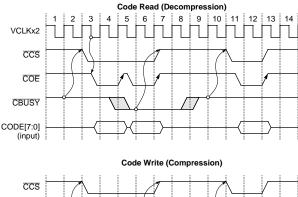

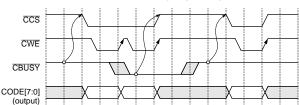

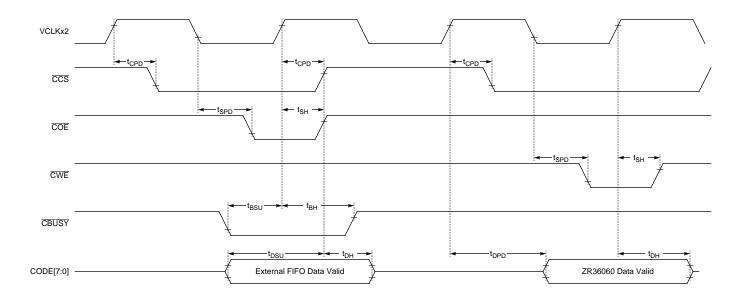

| CCS        | 0       | Code Chip Select, used only in Code Master mode. This active-low output signal acts as a chip select signal from the ZR36060 to the external code FIFO. $\overline{CCS}$ goes active at the start of a read or write cycle and remains active throughout the cycle. $\overline{CCS}$ remains active continuously in back to back read or write cycles.  During and after $\overline{RESET}$ this pin is logic high.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| COE        | 0       | Code Read (output enable), used only in Code Master mode. This active-low output signal acts as a read strobe signal from the ZR36060 to the external code FIFO. $\overline{\text{COE}}$ goes active 0.5 VCLKx2 cycles after start of a read cycle. The CODE bus input is latched on the rising edge of $\overline{\text{COE}}$ . During and after $\overline{\text{RESET}}$ this pin is logic high.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CWE        | 0       | Code Write, used only in Code Master mode. This active-low output signal acts as a write strobe signal from the ZR36060 to the external code FIFO. $\overline{\text{CWE}}$ goes active 0.5 VCLKx2 cycles after start of a write cycle. CODE bus data is valid throughout the strobe pulse and permits the external code FIFO to latch the data on the rising edge of $\overline{\text{CWE}}$ During and after $\overline{\text{RESET}}$ this pin is logic high.                                                                                                                                                                                                                                                                                                                                                                                 |

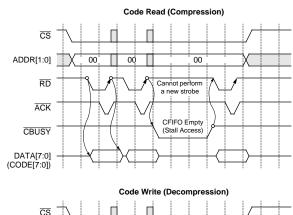

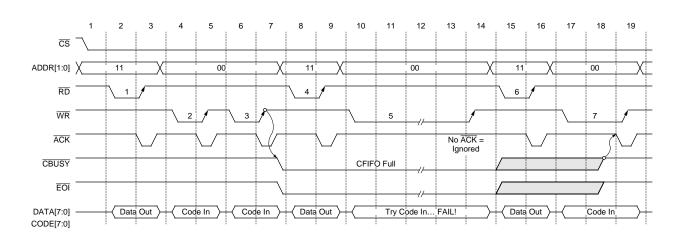

| CBUSY      | I/O     | Code FIFO Busy.  When the ZR36060 is the master of the code bus \(\overline{CBUSY}\) is an active-low input, used by the external code FIFO controller to temporarily halt the transfer of compressed data.  When the ZR36060 is the slave of the code bus \(\overline{CBUSY}\) is an active-low output. It is asserted (low) by the ZR36060 to indicate the internal code FIFO cannot be accessed, due to an empty/full condition (for compression/decompression modes respectively). On deassertion, \(\overline{CBUSY}\) is driven high for one internal clock and then released to a floating condition (needs external pullup).  When the ZR36060 is connected to the ZR36057, \(\overline{CBUSY}\) is connected to the \(\overline{CBUSY}\) input of the latter.  During and after \(\overline{RESET}\) his pin is floating (input mode). |

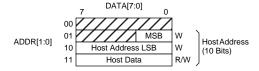

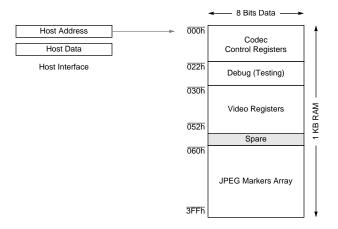

| DATA[7:0]  | I/O     | Data bus. This 8-bit bidirectional bus is used to read/write to the internal memory of the ZR36060.  In Code Slave mode, it is also used to transfer the compressed data. In 16-bit Code Slave mode, the CODE bus is used as an extension of the DATA bus.  During and after RESET this bus is floating with internal pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ADDR[1:0   | I       | Address bus. This 2-bit bus is used by the host to access the code register (in Code Slave mode), or the indirect address/data register which maps the 1Kbyte internal memory array of the ZR36060.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

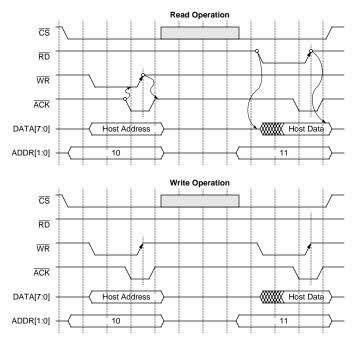

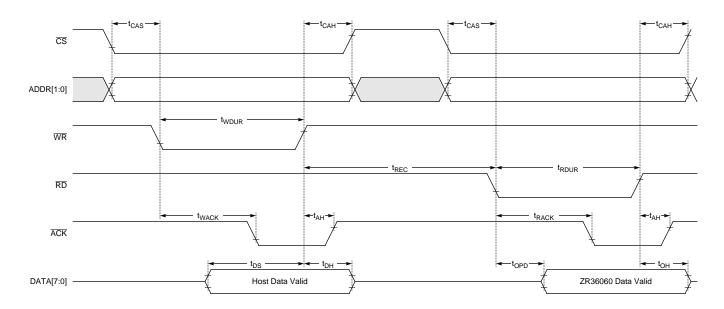

| CS         | ı       | Chip Select. This active-low input signal acts as a chip select signal from the host to the ZR36060.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WR         | I       | Write. This active-low input signal acts as a write pulse from the host to the ZR36060. The DATA (with CODE extension in 16-bit Code Slave mode), is latched on the rising edge of $\overline{\text{WR}}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RD         | I       | Read. This active-low input signal acts as a read pulse from the host to the ZR36060. The DATA (with CODE extension in 16-bit Code Slave mode), is enabled as an output during the $\overline{\text{RD}}$ pulse so the host can latch the ZR36060 data on the rising edge of $\overline{\text{RD}}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

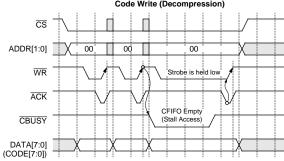

| ACK        | 0       | Acknowledge. Used by the ZR36060 to notify the host that the current read or write strobe pulse can be completed. During code access (Code Slave mode), the ZR36060 will not issue an $\overline{ACK}$ if the internal code FIFO is empty/full (in compression/decompression respectively). On deassertion, $\overline{ACK}$ ist driven high for 1 VCLKx2 cycle and then released to a floating condition (needs external pull-up). During and after $\overline{RESET}$ this pin is floating (logic high with pullup).                                                                                                                                                                                                                                                                                                                          |

| Video Port | (25 pin | s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

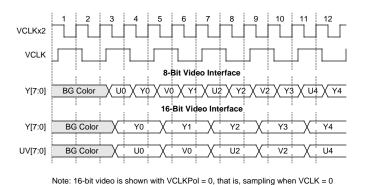

| Y7:Y0      | I/O     | In 16-bit video mode (Video8==0), these lines are the Luminance video lines. In 8-bit mode (Video8==1) these lines are luminance/chrominance lines, multiplexed in time according to the CCIR656 component order.  In compression these lines are inputs, while in decompression they are outputs.  During and after RESET this bus is floating with internal pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# **Table 1: Pin Descriptions (Continued)**

| Symbol    | Туре     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UV7:UV0   | I/O      | In 16-bit video mode (Video8==0), these lines are the chrominance video lines. In compression these lines are inputs, while in decompression they are outputs.  In 8-bit mode (Video8==1) these lines are not used: in compression they are ignored (inputs), and in decompression they are floating.  During and after RESET this bus is floating with internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

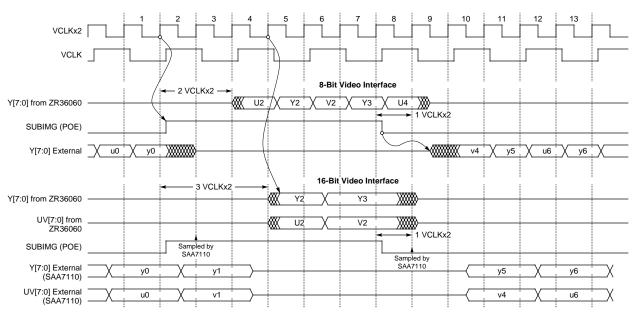

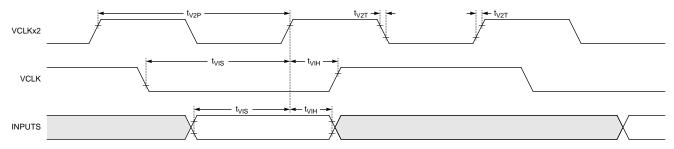

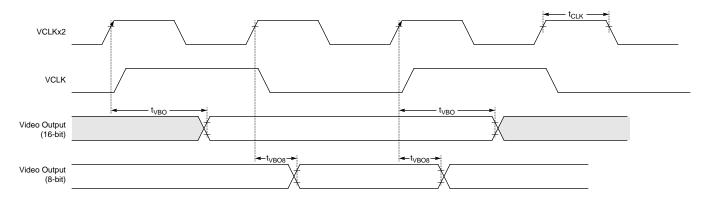

| VCLKx2    | ı        | Main Video Clock input. The video interface of the ZR36060 is synchronized by this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

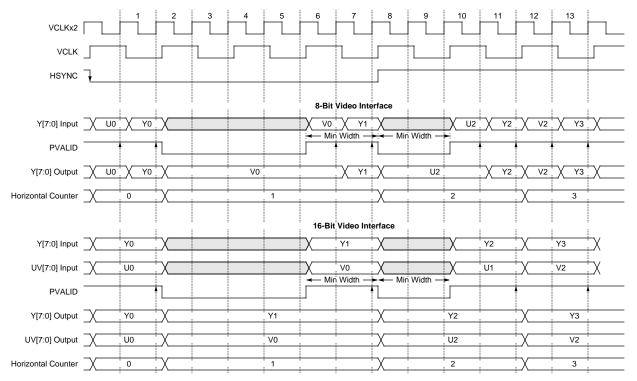

| VCLK      | I        | Digital video bus clock enable. Used as a qualifier of the video bus data. Must be synchronized and toggling at half the frequency of VCLKx2, in both 8 and 16-bit video bus width modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

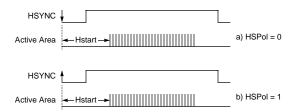

| HSYNC     | I/O      | Horizontal sync. When the ZR36060 is slave (SyncMstr==0), HSYNC is input, and when it is the sync master (SyncMstr==1) HSYNC is an output.  During and after RESET this pin is floating (input mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

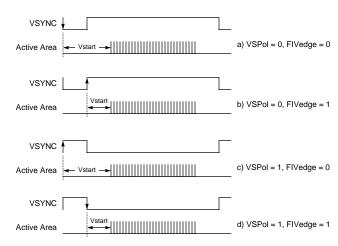

| VSYNC     | I/O      | Vertical sync. When the ZR36060 is slave (Syncstr==0), VSYNC is input, and when it is the sync master (SyncMstr==1) VSYNC is an output.  During and after RESET this pin is floating (input mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FI        | I/O      | Digital video bus field indicator (odd/even). When the ZR36060 is the master of the video bus FI is an output, otherwise it is an input. The polarity of FI, as input or output, is set by FiPol.  During and after RESET this pin is floating (input mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

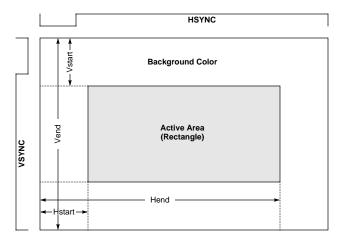

| BLANK     | 0        | Digital video bus composite blank output. Active only when the ZR36060 is the sync master of the video bus, otherwise the pin is floating. The horizontal and vertical blanking areas are programmable.  During and after RESET this pin is floating with internal pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PVALID    | I        | When the ZR36060 is in compression mode, this input is used as an additional qualifier (other than VCLK) of the video data signals and the sync signals. An active level sampled on this signal at the time when a pixel is sampled, indicates that this is a valid pixel. This input is meant to be connected to the $\overline{PXEN}$ output of the ZR36057.  When the ZR36060 is in decompression mode, this input is used by the recipient of the video to stall the video stream of the ZR36060. A non-active level sampled on this signal will cause the ZR36060 to continue to output the current pixel instead of proceeding to the next one. Once PVALID is sampled active again the normal pixel sequence resumes.  If the ZR36060 is the video sync master, then PVALID not active will freeze the internal sync generator. The polarity of PVALID can be programmed. |

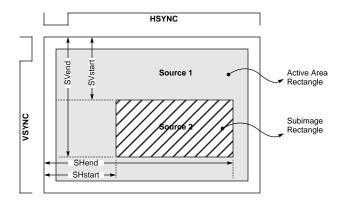

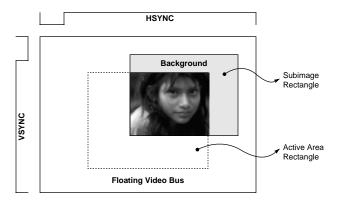

| SUBIMG    | 0        | This output dynamically indicates the boundaries of a sub-image rectangle within the main input or output field size. When the pixels within the programmable rectangle are output/input, SUBIMG is active. For a sub-line of consecutive pixels within the rectangle, SUBIMG is continuously active. The polarity of SUBIMG is programmable.  SUBIMG may be connected to the FEIN input of the SAA7110/11, or the read-enable input of a line buffer, FIFO, etc., to permit pixel-by-pixel video mixing during compression and decompression.  During and after RESET this pin is logic high.                                                                                                                                                                                                                                                                                   |

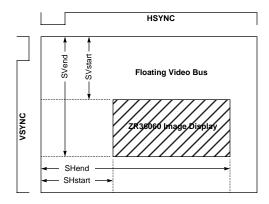

| POE       | ı        | Pixel Output Enable. Used to disable the video bus during decompression, to permit pixel-by-pixel video mixing of the ZR36060 video output with another source. It can be directly connected to the SUBIMG output, or to other suitable control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Control & | Status ( | 10 pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

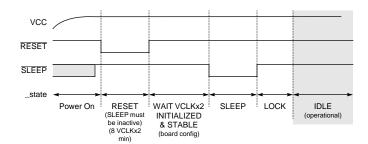

| RESET     | I        | Reset. When this input is asserted the ZR36060 goes into its RESET state. When it is deasserted all state machines are in IDLE mode and registers contain their default values. RESET must be active for at least 8 VCLKx2 cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SLEEP     | I        | Power-down mode. When this input is active (low), the ZR36060 goes into its SLEEP (power-down) mode, discontinuing all chip operation and consuming minimal supply current.  This pin also initiates coarse locking of the internal PLL to the VCLKx2 frequency. It must be toggled at least once after RESET.  SLEEP must remain low for at least 8 VCLKx2 cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

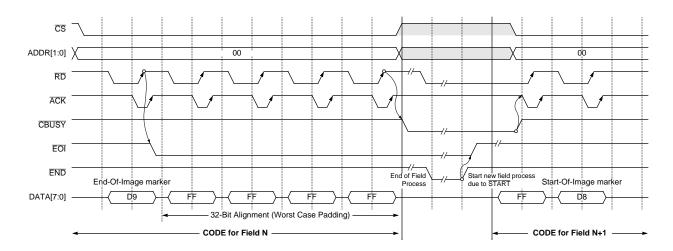

| END       | 0        | End of process indication. This active-low output signal indicates completion of a field compression/decompression process. During and after RESET this pin is logic low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ĒŌĪ       | 0        | End-of-image marker indication. This active-low output signal indicates the last code byte, or word (FFD8 code) is being output or input. $\overline{EOI}$ is deasserted together with the deassertion (rising edge) of $\overline{END}$ upon beginning of the next field process. During and after $\overline{RESET}$ this pin is logic low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| START     | I        | Start compression/decompression command input. When the ZR36060 is in IDLE state, it looks for an active low level on this input in order to start compression or decompression. Once the active level is sampled the ZR36060 will start compression or decompression with the next VSYNC or with the next odd VSYNC (depending on the FRAME input).  To be detected correctly, START must remain low for at least 2 VCLKs.  When the ZR36060 is connected to the ZR36057, this input must be connected to a GCS output of the ZR36057.                                                                                                                                                                                                                                                                                                                                          |

| FRAME     | I        | This input is sampled by the ZR36060 together with the START input. When START is sampled active, then if FRAME is also active the ZR36060 will start compressing/decompressing at the next odd field. Otherwise it will start with the next field.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# **Table 1: Pin Descriptions (Continued)**

| Symbol          | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATERR          | 0    | This output is asserted when there is a data corruption event. It is deasserted together with the deassertion (rising edge) of END upon beginning of the next field process. On deassertion, DATERR is floating (needs external pull-up).  During and after RESET this pin is floating (logic high with pullup).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RTBSY           | 0    | In compression this output signal indicates a "nearly full" condition in the internal raster-to-block memory ("strip" buffer). This condition occurs when the strip buffer is 16 (or fewer) pixels away from an overflow condition.  In decompression RTBSY indicates that the strip buffer is nearly empty, i.e., during every 8*n line of video there are enough blocks to display the next video line. Otherwise an underflow condition occurs.  In IDLE state RTBSY is not asserted.  If while RTBSY is asserted a data corruption event occurs (overflow or underflow), RTBSY continues to be asserted together with DATERR until the beginning of the next field process (deassertion of END). If no data corruption occurs, RTBSY is deasserted as soon as the almost-overflow/underflow condition is no longer true.  RTBSY is meant to be connected to the RTBSY input of the ZR36057.  During and after RESET this pin is a logic high. |

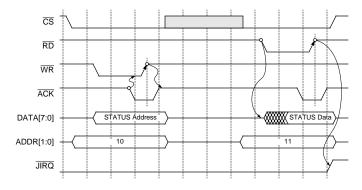

| JIRQ            | 0    | Interrupt request (active low). This output signal requests an interrupt from the host controller, if an interrupt request is enabled and one of the events associated with interrupts occurs. It is deasserted if the host responds to the interrupt by reading the interrupt status register, or if the host disables the interrupt, or upon a reset to the ZR36060.  On deassertion JIRQ is floating (needs external pull-up).  When JIRQ is active, the START signal is disregarded.  During and after RESET this pin is floating (logic high).                                                                                                                                                                                                                                                                                                                                                                                               |

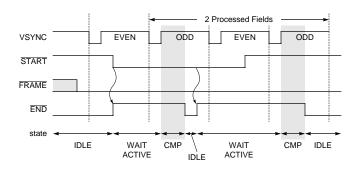

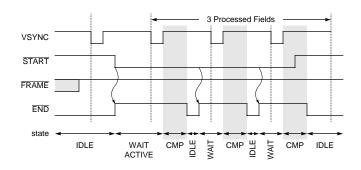

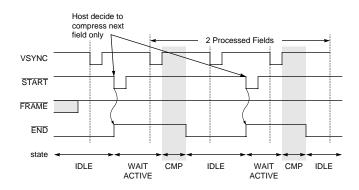

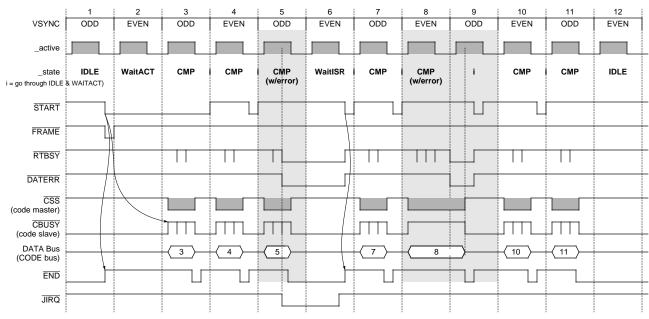

| COMP            | 0    | Compress/Decompress. This output signal provides an indication of the current operating mode of the ZR36060. When it is high, the ZR36060 is in the compression mode; when it is low, the ZR36060 is in the decompression mode.  During and after RESET this pin is a logic high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |